引言

對于攻讀微電子、集成電路等相關專業的國科大學子而言,《超大規模集成電路設計》是一門兼具理論深度與工程實踐挑戰的核心課程。期末考試不僅是對知識體系的系統檢驗,更是對設計思維與問題解決能力的綜合評估。一份高效的復習計劃,能夠幫助同學們提綱挈領,從容應考。

一、 核心知識模塊梳理

1. VLSI設計流程與設計方法學

這是課程的宏觀框架。務必掌握從系統規范、邏輯設計、電路設計、物理設計到制造測試的完整流程。理解自頂向下(Top-Down)與自底向上(Bottom-Up)設計方法,以及它們在現代SoC(片上系統)設計中的融合應用。

2. CMOS制造工藝與版圖設計

- 回顧CMOS制造的關鍵步驟(光刻、刻蝕、離子注入、淀積等)。

- 深入理解設計規則(Design Rules)的內涵,包括線寬、間距、覆蓋等約束,并能解讀簡單的設計規則文件。

- 熟練掌握基本器件(反相器、與非門、或非門)的版圖繪制,理解有源區、多晶硅、金屬層、接觸孔和通孔的作用。

- 掌握“棍棒圖”(Stick Diagram)作為連接電路圖與版圖的橋梁作用。

3. CMOS電路特性與性能分析

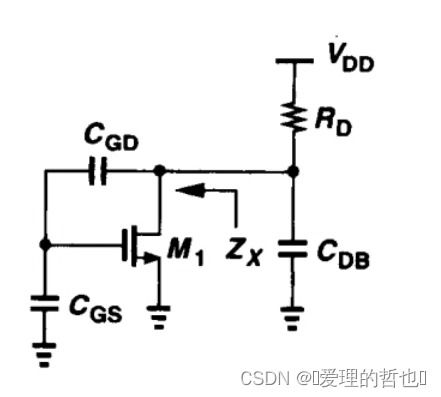

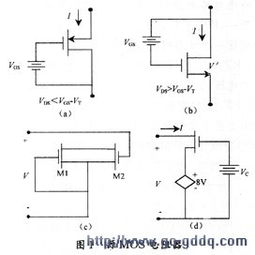

- 靜態特性:深刻理解電壓傳輸特性(VTC)、噪聲容限、開關閾值。

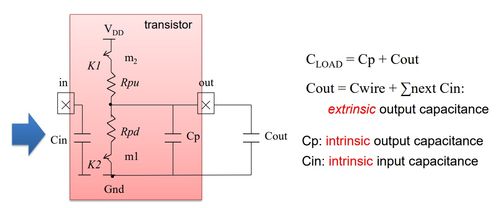

- 動態特性:這是重中之重。熟練掌握延時(傳播延時、上升/下降時間)的計算方法,理解其與負載電容、晶體管尺寸(W/L)、電源電壓的依賴關系。

- 功耗分析:清晰區分動態功耗、靜態功耗(漏電流)和短路功耗的來源與估算公式。低功耗設計技術(如電源門控、多閾值電壓技術、動態電壓頻率調節DVFS)是常考點。

4. 組合邏輯與時序邏輯電路設計

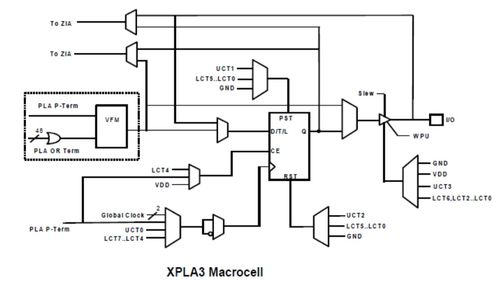

- 組合邏輯:掌握靜態CMOS、有比邏輯(如偽NMOS)、傳輸管邏輯、動態邏輯(Domino邏輯)等不同電路結構的原理、優缺點和典型應用場景。

- 時序邏輯:重點掌握鎖存器(Latch)和觸發器(Flip-Flop)的電路結構(如傳輸門結構、主從結構)、工作原理、時序參數(建立時間、保持時間、時鐘到輸出延時)。

5. 存儲器與互連線

- 存儲器:了解SRAM(6T單元)和DRAM(1T1C單元)的基本存儲單元結構、讀寫操作原理及外圍電路(如靈敏放大器、行列譯碼器)的作用。

- 互連線:理解互連線寄生參數(電阻R、電容C、電感L)對信號完整性、延時和功耗的影響。掌握Elmore延時模型用于估算RC樹網絡延時。

6. 設計驗證與測試

- 了解功能驗證、時序驗證、物理驗證(DRC, LVS)的基本概念。

- 掌握可測性設計(DFT)中的基本概念,如掃描鏈(Scan Chain)的原理與插入方法。

二、 復習策略與重點

- 回歸教材與課件:以課程指定教材(如Rabaey的《數字集成電路設計》)和課堂PPT為核心,系統回顧每個章節。課件中的例題和推導過程往往是考試重點的映射。

- 攻克計算與分析題:

- 延時計算(反相器鏈、邏輯門)、功耗估算、噪聲容限求解是計算題的常客。務必親手推導和練習,熟悉公式應用場景。

- 能夠分析給定電路圖的工作原理、時序特性,并識別潛在問題(如競爭冒險、電荷分享等)。

- 理解版圖與電路圖的對應關系:能夠根據簡單的電路圖畫出對應的“棍棒圖”或示意性版圖,反之亦然。這是考察空間思維和工藝理解能力的關鍵。

- 關注設計權衡(Trade-off):VLSI設計的精髓在于在速度(性能)、面積、功耗之間取得平衡。復習時要有意識地將不同技術(如邏輯風格選擇、晶體管尺寸縮放)放在這個三維空間中進行對比思考。

- 研習歷年真題與作業題:在掌握基礎知識后,通過真題模擬考試環境,查漏補缺。重點分析錯題,理解背后的原理,而非死記答案。

三、 復習時間建議

- 第一階段(知識回顧,約1周):按模塊通讀教材與課件,整理個人筆記,形成知識樹。

- 第二階段(深化理解與練習,約1周):集中攻克重點難點,完成課后習題和作業題,強化計算與分析能力。

- 第三階段(模擬與沖刺,約3-5天):進行真題模擬,限時完成,檢驗復習效果。針對薄弱環節進行最后強化,復習所有整理過的公式、概念和設計規則。

##

超大規模集成電路設計是一門充滿智慧與創造性的學科。期末考試只是學習過程中的一個節點,其根本目的在于促使大家系統性地構建起從晶體管到復雜系統的設計知識體系。保持清晰的邏輯,注重理解而非死記,將每個知識點置于實際設計的語境中去思考,方能舉一反三,游刃有余。預祝各位國科大學子復習順利,在考場上展現出扎實的學識與卓越的工程素養!